- INDEX目次

目次【非表示】

- 1.半導体デバイスにおけるゲート絶縁膜の重要な役割

- 1-1.ゲート電極とチャネルを電気的に絶縁する

- 1-2.ゲート電圧を効率的に伝達しトランジスタを制御する

- 1-3.リーク電流を抑えデバイスの信頼性を確保する

- 2.ゲート絶縁膜に求められる特性とは

- 2-1.高い絶縁耐圧と低いリーク電流

- 2-2.良質な界面特性で安定した動作を実現

- 2-3.微細化に対応できる薄さと均一性

- 3.ゲート絶縁膜に使われる代表的な材料

- 3-1.長年使用されてきた二酸化ケイ素(SiO2)

- 3-2.性能向上に不可欠な高誘電率材料(High-k材料)

- 4.高品質なゲート絶縁膜を形成するための主な成膜方法

- 4-1.熱酸化法による成膜プロセス

- 4-2.CVD法を用いた均一な薄膜形成

- 4-3.ALD法による原子レベルでの精密な膜厚制御

- 5.次世代半導体で期待されるゲート絶縁膜の技術動向

- 6.まとめ

ゲート絶縁膜とは、半導体デバイスのトランジスタにおいて、ゲート電極とチャネルの間を隔てる非常に薄い絶縁体の膜のことです。この膜は、電圧を印加するゲート電極と、電流が流れるチャネル領域とを電気的に分離し、電流の流れを制御する重要な役割を担っています。特に、mosfetのような電界効果トランジスタでは、ゲート絶縁膜の性能がデバイス全体の特性を大きく左右します。近年では、デバイスの高性能化と微細化の進展に伴い、ゲート絶縁膜の薄膜化が重要な課題となっており、より薄く、かつ高い絶縁性を保持できる材料や成膜技術の開発が活発に進められています。

半導体デバイスにおけるゲート絶縁膜の重要な役割

ゲート絶縁膜は、半導体デバイスであるトランジスタの性能を左右する極めて重要な薄膜です。この膜は、ゲート電極とチャネル領域を電気的に絶縁することで、電流が不必要に流れるのを防ぐ役割を果たしています。これにより、トランジスタのオン/オフ動作を正確に制御し、デバイスが安定して機能することを可能にしています。

また、ゲート絶縁膜は、ゲート電圧を効率的にチャネルに伝えることで、トランジスタのスイッチング速度や消費電力といった電気特性に直接影響を与えます。さらに、リーク電流を最小限に抑え、デバイスの信頼性と耐久性を高める上でも不可欠な存在です。そのため、半導体デバイスの高性能化と省電力化には、高品質なゲート絶縁膜が欠かせません。

ゲート電極とチャネルを電気的に絶縁する

トランジスタの基本的な機能は、電気信号のオンとオフを切り替えるスイッチング動作です。この動作を実現するために、ゲート電極とチャネルの間には、電気を流さない「ゲート絶縁体」と呼ばれる非常に薄い絶縁膜が設けられています。ゲート絶縁体は、ゲート電極とチャネルが直接接触して電流が流れる「短絡」を防ぐだけでなく、ゲート電圧がチャネルに効率的に伝わり、トランジスタのオン/オフを正確に制御するために不可欠な存在です。もしこの絶縁が不十分だと、ゲート電極とチャネル間で不要な電流が漏れてしまい、トランジスタが正常に動作しなくなります。特に、半導体デバイスの微細化が進むにつれて、ゲート絶縁体の膜厚は原子数層レベルまで薄くなっており、その絶縁性能の確保はますます重要になっています。高い絶縁性を保ちつつ、安定した動作を維持することが、半導体デバイスの性能と信頼性を決定づける重要な要素となるのです。

ゲート電圧を効率的に伝達しトランジスタを制御する

トランジスタは、半導体のオン/オフを切り替えることで電流を制御するスイッチのような役割を担っています。ゲート絶縁膜は、このトランジスタの制御において重要な役割を果たしており、ゲート電極に印加された電圧を効率的にチャネル領域へ伝達することで、トランジスタの動作を安定させるのです。具体的には、ゲート絶縁膜がゲート電極とチャネルの間で高い絶縁性を持つことにより、ゲート電圧がチャネルの電気的な特性に直接影響を与え、電流の通り道であるチャネルの導電性を制御します。ゲート絶縁膜が十分に薄く、かつ均一であるほど、ゲート電圧の変化に対してチャネルが敏感に反応し、より高速かつ正確なトランジスタの制御が可能となります。例えば、高性能なCPUやメモリでは、ゲート絶縁膜のわずかな厚さのばらつきがデバイス全体の性能に大きく影響するため、ナノメートルオーダーでの精密な膜厚制御が求められます。このような効率的なゲート電圧の伝達は、半導体デバイスの高速動作や低消費電力化に直結するため、ゲート絶縁膜の性能がデバイス全体の性能を左右すると言っても過言ではありません。さらに、ゲート絶縁膜は高い耐圧性能も求められ、デバイスの安定稼働に不可欠な要素です。

リーク電流を抑えデバイスの信頼性を確保する

ゲート絶縁膜は、ゲート電極とチャネル間の不要な電流、つまりリーク電流を防ぐ重要な役割を担っています。このリーク電流が発生すると、デバイスの消費電力が増加するだけでなく、誤動作や発熱の原因となり、最終的にはデバイスの信頼性や寿命を著しく低下させてしまいます。特に、近年ますます微細化が進む半導体デバイスにおいては、ゲート絶縁膜の厚さが原子レベルにまで薄くなっているため、リーク電流の抑制は喫緊の課題となっています。例えば、10nm以下のゲート長を持つトランジスタでは、量子トンネル効果によるリーク電流が顕著になり、デバイス性能を大きく左右します。このリーク電流を効果的に抑えるためには、ゲート絶縁膜の厚さを均一に制御し、膜質の欠陥を極限まで減らすことが不可欠です。さらに、高誘電率材料(High-k材料)の導入により、物理的な厚さを保ちつつ実効的な厚さを薄くすることで、リーク電流を抑制し、同時にゲート容量を確保することが可能になります。これにより、デバイスの安定した動作と長寿命化が実現され、スマートフォンやPCなどの電子機器の性能向上に貢献しています。

ゲート絶縁膜に求められる特性とは

ゲート絶縁膜には、高い絶縁耐圧と低いリーク電流が求められます。これは、ゲート電極とチャネル間での不要な電流の流れを防ぎ、トランジスタの安定した動作を保証するために不可欠です。

また、良質な界面特性も重要であり、ゲート絶縁膜と半導体材料との間に欠陥が少ないことが望まれます。これにより、ゲート電圧の変化に対してチャネルが効率的に応答し、安定したデバイス動作が可能になります。さらに、半導体デバイスの微細化に対応するためには、ゲート絶縁膜が極めて薄く、かつ均一であることも重要な特性です。これにより、高密度な集積回路の実現と、デバイス性能の向上に貢献します。

高い絶縁耐圧と低いリーク電流

ゲート絶縁膜は、ゲート電極とチャネル間の電気的絶縁を保ち、リーク電流を抑制する役割があります。この役割を果たすためには、高い絶縁破壊電界強度(絶縁耐圧)と低いリーク電流が不可欠です。絶縁耐圧とは、ゲート絶縁膜が電気的に破壊されることなく耐えられる最大電界強度を指します。絶縁耐圧が高いほど、ゲート絶縁膜はより高い電圧に耐えられ、デバイスの信頼性が向上します。また、リーク電流は、ゲート絶縁膜を介して流れる不要な電流であり、これはデバイスの消費電力の増加や誤動作の原因となるため、可能な限り低く抑える必要があります。

近年、半導体デバイスの微細化が進むにつれて、ゲート絶縁膜の厚さは原子数層レベルまで薄くなっています。しかし、膜厚を薄くすると、量子力学的なトンネル効果によりリーク電流が増加するという問題が生じます。この課題を解決するために、二酸化ケイ素(SiO2)に代わる高誘電率(high-k)材料の導入が進められています。高誘電率材料は、二酸化ケイ素よりも高い誘電率を持つため、同じ膜厚であってもより高い静電容量を得ることができ、実効的な膜厚を厚くしながら、デバイスの性能を維持することが可能です。これにより、リーク電流の抑制と高い絶縁耐圧の両立を実現しています。

良質な界面特性で安定した動作を実現

ゲート絶縁膜の性能は、半導体デバイスの安定した動作に不可欠であり、特に界面特性の良し悪しが大きく影響します。界面特性とは、ゲート絶縁膜と半導体基板との境界領域における電気的・物理的な性質を指し、この界面の欠陥が少ないほど、デバイスは安定して動作します。例えば、界面に電荷トラップとなる欠陥が存在すると、トランジスタの閾値電圧が変動したり、移動度が低下したりして、デバイス性能が不安定になる原因となります。

良質な界面特性を実現するためには、成膜プロセスにおいて界面の不純物混入を極力抑え、化学的に安定した構造を形成することが重要です。特に、シリコンカーバイド(sic)などの次世代パワー半導体においては、高温・高電力環境下での安定動作が求められるため、ゲート絶縁膜とsic基板との界面品質がさらに重要視されます。sic半導体デバイスでは、従来のシリコン(Si)基板に比べてバンドギャップが広く、絶縁破壊電界も高いため、より薄いゲート絶縁膜でも高い絶縁耐圧を確保できますが、その分、界面のわずかな欠陥がデバイス特性に大きな影響を与える可能性があります。

そのため、ゲート絶縁膜の成膜後には、アニール処理などの熱処理を施すことで界面の欠陥を低減し、電気的特性を改善する取り組みが広く行われています。このように、良質な界面特性は、ゲート絶縁膜のリーク電流の抑制や、ゲート電圧に対するチャネル電流の応答性を高め、結果としてトランジスタの安定した動作と高い信頼性を実現するために不可欠な要素と言えるでしょう。

微細化に対応できる薄さと均一性

半導体デバイスの微細化は、集積度と性能向上に不可欠な要素です。ゲート絶縁膜も、この微細化のトレンドに対応するために、より薄く、より均一な膜厚が求められています。たとえば、最先端のロジックデバイスでは、ゲート絶縁膜の厚さが原子数層レベルにまで薄くなっています。これは、ゲート長が短くなるにつれて、ゲート電極とチャネル間の距離も縮小する必要があるためです。ゲート絶縁膜が薄いほど、ゲート電圧をより効率的にチャネルに伝え、トランジスタのスイッチング速度を向上させることができます。しかし、膜厚が薄くなるにつれて、リーク電流が増加しやすくなるという課題も生じます。そのため、薄膜化と同時に、高い絶縁性や低リーク電流特性を維持することが極めて重要となります。

また、ゲート絶縁膜の膜厚の均一性も、デバイス性能に大きく影響します。もし膜厚にばらつきがあると、トランジスタごとの特性に差が生じ、回路全体の動作が不安定になる可能性があります。特に、何十億ものトランジスタが集積されたLSIでは、ゲート絶縁膜の均一性がデバイスの歩留まりや信頼性を左右する重要な要素となります。現在の製造プロセスでは、数ナノメートルオーダーの膜厚を、ウェーハ全面にわたって±数原子層レベルで均一に形成する技術が求められています。原子層堆積(ALD)法などの成膜技術が、この微細化と均一性の要求に応える鍵となっています。

ゲート絶縁膜に使われる代表的な材料

ゲート絶縁膜には、長年にわたり二酸化ケイ素(SiO2)が主要な材料として利用されてきました。しかし、半導体デバイスの微細化が進むにつれて、二酸化ケイ素だけでは性能維持が困難になっています。そこで、高誘電率材料(High-k材料)が導入され、ゲート絶縁膜の性能向上に貢献しています。この二酸化ケイ素と高誘電率材料は、それぞれの特性を活かして、半導体デバイスの発展を支えています。

長年使用されてきた二酸化ケイ素(SiO2)

二酸化ケイ素(SiO2)は、半導体デバイスのゲート絶縁膜として長年にわたり広く使用されてきました。その歴史は古く、1960年代のプレーナ型MOSFETの発明以来、半導体産業の発展を支える基幹材料として不可欠な存在です。SiO2が選ばれてきた主な理由としては、シリコン基板との優れた界面特性が挙げられます。シリコンとSiO2の界面は電気的に安定しており、電子の移動を妨げることなくスムーズな電流制御を可能にします。また、高い絶縁耐圧を持ち、ゲート電極とチャネル間の漏れ電流を効果的に抑制する能力に優れています。さらに、その成膜方法も確立されており、熱酸化法という比較的シンプルなプロセスで高品質な膜を形成できる点も大きな利点でした。熱酸化法は、シリコンウェハーを高温の酸素雰囲気下で処理することで、表面にSiO2膜を成長させる方法です。この方法は、原子レベルで平坦な界面を形成できるため、信頼性の高いゲート絶縁膜を実現してきました。しかし、半導体デバイスの微細化が進むにつれて、SiO2の物理的な限界が顕在化してきました。特に、ゲート長が数十ナノメートル以下になると、SiO2膜を薄くする必要があり、その結果、量子トンネル効果によるリーク電流が増加するという課題が生じています。このリーク電流の増加は、デバイスの消費電力の増大や信頼性の低下に直結するため、SiO2に代わる新しい材料の開発が求められるようになりました。

性能向上に不可欠な高誘電率材料(High-k材料)

トランジスタの微細化と高性能化が進むにつれて、従来の二酸化ケイ素(SiO2)ではゲート絶縁膜の性能維持が困難になってきました。そこで登場したのが、高誘電率材料、通称High-k材料です。High-k材料は、その名の通り誘電率が高く、同じ膜厚であればSiO2よりも多くの電荷を蓄えることができます。これにより、ゲート電極とチャネル間の容量を効率的に高め、トランジスタのスイッチング性能を向上させることが可能となります。具体的には、High-k材料を使用することで、実効的な膜厚を維持しつつ物理的な膜厚を厚くできるため、リーク電流の発生を抑制し、デバイスの消費電力低減に貢献します。インテル社は2007年にはすでにHigh-k材料であるハフニウム系材料をゲート絶縁膜に導入し、45nm世代のCPU量産に成功しています。現在では、ハフニウム酸化物(HfO2)やジルコニウム酸化物(ZrO2)などが主要なHigh-k材料として実用化されており、これらは高い誘電率と熱安定性を持ち、ゲート絶縁膜としての厳しい要求特性を満たしています。High-k材料の導入は、半導体デバイスのさらなる微細化と性能向上、低消費電力化に不可欠な技術要素であり、今後の半導体産業の発展においてもその重要性は増すばかりです。

高品質なゲート絶縁膜を形成するための主な成膜方法

高品質なゲート絶縁膜を形成するための主な成膜方法として、熱酸化法、CVD法、ALD法が挙げられます。熱酸化法は、シリコンウェーハを高温の酸素や水蒸気などの酸化性雰囲気で加熱し、シリコン表面を酸化させて二酸化ケイ素(SiO2)膜を形成する方法です。この方法は、MOSデバイスのゲート絶縁膜や、キャパシタ用絶縁膜の作成に不可欠な技術となっています。熱酸化法で形成される酸化膜は非常に安定しており、均一で欠陥が少ない高品質な膜が得られるという特長があります。しかし、水分やアルカリ金属などの不純物が酸化膜中に混入すると、デバイス特性が変動する可能性があるため、CVD法で形成した不活性化絶縁膜で覆うことで不純物の侵入を阻止することが重要です。熱酸化には、使用するガスの種類や形態によってドライ酸化やウェット酸化といった種類があります。

熱酸化法による成膜プロセス

熱酸化法は、シリコンウェハーを高温の酸素または水蒸気雰囲気にさらすことで、ウェハー表面に二酸化ケイ素(SiO2)膜を形成するプロセスです。この方法は、半導体デバイスのゲート絶縁膜形成において長年にわたり広く用いられてきました。特に、MOSFET(金属酸化膜半導体電界効果トランジスタ)のゲート絶縁膜は、この熱酸化法によって作製されることが多いです。熱酸化法は、シリコンと酸化膜の界面における電気的特性が非常に優れているという大きな特徴があります。これは、シリコン原子と酸素原子が直接結合し、結晶構造の不整合が少ないため、界面準位と呼ばれる欠陥が極めて少ないことが理由として挙げられます。界面準位が少ないことで、ゲート電圧の印加に対するチャネルの応答性が向上し、トランジスタの安定した動作に貢献します。また、熱酸化膜は電気絶縁性に優れ、高い絶縁破壊電界強度を持つため、リーク電流を効果的に抑制し、デバイスの信頼性を高めることが可能です。さらに、成膜プロセス自体が比較的単純で、高い再現性を持つこともメリットです。しかし、熱酸化法には高温プロセスが必要となるため、熱バジェットの制約や、膜厚の微細な制御が難しいという課題も存在します。特に、デバイスの微細化が進むにつれて、より薄く、より均一なゲート絶縁膜が求められるため、これらの課題を克服するための研究開発が継続的に行われています。例えば、低温での熱酸化技術や、より精密な膜厚制御を可能にするプロセスの改良などが進められています。

CVD法を用いた均一な薄膜形成

CVD法(化学気相成長法)は、薄膜を形成する代表的な方法の一つです。この方法では、成膜したい物質の原料となるガスを基板に供給し、熱やプラズマ、光などのエネルギーによって化学反応を起こさせることで、基板表面に薄膜を堆積させます。CVD法は、半導体の絶縁膜や保護膜の形成に広く用いられており、例えばシリコン酸化膜や窒化シリコン膜の形成にも活用されています。

CVD法の大きな特徴は、その均一な成膜性です。原料ガスをチャンバー内に充満させて加工するため、複雑な形状の基板や微細な凹凸がある場合でも、比較的均一な膜を形成できます。また、成膜速度が速く、大量生産にも適しているというメリットもあります。

CVD法には、熱CVD法、プラズマCVD法、光CVD法など、原料ガスの分解方法によっていくつかの種類があります。熱CVD法は、高温でガスを反応させることで膜を形成し、比較的単純な装置構成で均一な膜厚分布が得られます。プラズマCVD法は、プラズマを用いて原料ガスを活性化させるため、熱CVD法よりも低い温度での成膜が可能となり、基板への熱ダメージを抑えることができます。

ゲート絶縁膜の形成においては、CVD法を用いることで、膜厚や組成、結晶性、密着性、応力といった多くの成膜条件を制御できます。これにより、デバイスの性能や信頼性を左右する高品質なゲート絶縁膜の形成が可能となります。

ALD法による原子レベルでの精密な膜厚制御

原子層堆積(ALD)法は、原子レベルでの精密な膜厚制御を可能にする成膜技術です。この方法は、半導体デバイスの微細化と高性能化に不可欠な技術として注目されています。ALD法は、主に2種類のガス状の化学物質(プリカーサ)を交互に基板表面に導入し、自己制御的な化学反応によって原子を一層ずつ堆積させることで薄膜を形成します。これにより、極めて薄く、均一で緻密な膜を形成できる点が大きな特徴です。

ALD法のプロセスは、一般的に4つのステップからなるサイクルを繰り返します。まず、第1前駆体ガスを導入し、基板表面に自己制限的に吸着させます。次に、余分なガスをパージ(排出)します。その後、第2前駆体ガス(反応ガス)を導入し、吸着した第1前駆体と反応させて目的の薄膜の原子1層分を形成します。最後に、再び余分なガスをパージします。このサイクルを繰り返すことで、膜厚を原子層単位で正確に制御できるのです。

この技術の最大の利点は、複雑な3D構造や高アスペクト比の基板に対しても、非常に高い段差被覆性(コンフォーマル性)で均一な膜を形成できることです。そのため、従来の成膜方法では困難だった微細な構造を持つ半導体デバイス、特にゲート絶縁膜の形成に広く応用されています。例えば、高性能トランジスタのゲート絶縁膜として使用される酸化ハフニウム(HfO₂)膜や、酸化アルミニウム(Al₂O₃)膜などの高誘電率(High-k)材料の形成にALD法が活用されています。

ALD法は、低温での成膜も可能であるため、熱に敏感な材料への適用や、熱によるデバイス性能の低下を抑制できるというメリットもあります。一方で、成膜速度が遅い、高真空が必要、装置コストが高いといった課題も存在します。しかし、半導体デバイスのさらなる微細化と高性能化の要求が高まるにつれて、ALD技術の重要性はますます増していくと考えられています。

次世代半導体で期待されるゲート絶縁膜の技術動向

次世代半導体技術において、ゲート絶縁膜は性能向上と低消費電力化の鍵を握る要素です。特に、トランジスタの微細化が進む中で、従来の二酸化ケイ素(SiO2)に代わる新しい材料や構造の開発が活発に進められています。

現在注目されている技術動向の一つは、高誘電率(High-k)材料とメタルゲートを組み合わせた「High-k/Metalゲート技術」です。従来のSiO2膜では、15nm以下の微細化でリーク電流が顕著になる課題がありましたが、High-k材料は物理的な膜厚を厚くしつつ、電気的には薄く見せることでリーク電流を抑制します。具体的には、ハフニウム酸化膜(HfO2)系の材料が広く使われており、メタルゲートには窒化タンタル(TaN)や窒化チタン(TiN)などが用いられます。この技術は、微細化に伴うゲートリーク電流の抑制と、高速動作、低消費電力化に大きく貢献しています。Intelは45nmプロセスでHigh-k/メタルゲート技術を初めて採用し、その後のCMOS微細化を推進しました。また、東京工業大学などの研究チームは、酸化ランタン(La2O3)をHigh-kゲート絶縁膜として使用し、実効ゲート絶縁膜厚0.37nmのトランジスタ作製に成功しています。

さらに、パワー半導体の分野では、炭化ケイ素(SiC)や窒化ガリウム(GaN)といったワイドバンドギャップ半導体を用いたデバイスの開発が進んでおり、ここでもゲート絶縁膜の技術革新が不可欠です。GaNパワー半導体では、ゲート絶縁膜中の不純物トラップがしきい値電圧変動の原因となるため、不純物を極限まで低減するプロセス技術が東芝によって開発されました。この技術により、GaN-MOSFETの信頼性が向上し、GaNパワーデバイスの普及が期待されています。また、SiCパワーデバイスにおいては、ゲート絶縁膜であるSiO2とSiCの界面に生成する欠陥を低減する技術が東京大学によって開発され、高品質な界面を実現しています。

メモリ分野では、3D NANDフラッシュメモリにおいて、セルストリングを垂直方向に積層する構造が採用されており、ゲート絶縁膜も電荷捕獲(チャージトラップ)構造という酸化シリコン膜と窒化シリコン膜の複合的な構造に変化しています。東芝が開発した「BiCS」技術やSamsungの「TCAT」技術では、メモリスルーホールと呼ばれる細長い孔の内壁に電荷を捕獲する絶縁層(シリコン窒化膜)を均一に成膜し、超大容量化を実現しています。

これらの技術動向は、次世代半導体デバイスのさらなる高性能化、低消費電力化、そして高信頼性化を実現するために、ゲート絶縁膜の材料、構造、および成膜方法における継続的な進化を示しています。

まとめ

ゲート絶縁膜は、トランジスタの性能を左右する重要な要素です。ゲート電極とチャネルを電気的に絶縁し、ゲート電圧を効率的に伝達することで、トランジスタの安定した動作を可能にしています。微細化が進む半導体デバイスにおいて、ゲート絶縁膜には高い絶縁耐圧と低いリーク電流、良好な界面特性、そして均一な薄さが求められています。

これらの特性を実現するため、古くから二酸化ケイ素(SiO2)が使用されてきましたが、近年では高誘電率(High-k)材料の採用が進んでいます。 成膜方法も、熱酸化法に加えてCVD法やALD法が用いられ、原子レベルでの精密な膜厚制御が可能になっています。 今後も、低消費電力化や高性能化に対応するため、ゲート絶縁膜の材料開発やプロセス技術の革新が重要な研究分野であり続けるでしょう。

西進商事コラム編集部

西進商事コラム編集部です。専門商社かつメーカーとしての長い歴史を持ち、精密装置やレーザー加工の最前線を発信。分析標準物質の活用も含め、さまざまなコラム発信をします。

2nmプロセスとは?次世代半導体の仕組みや製造が難しい理由を解説

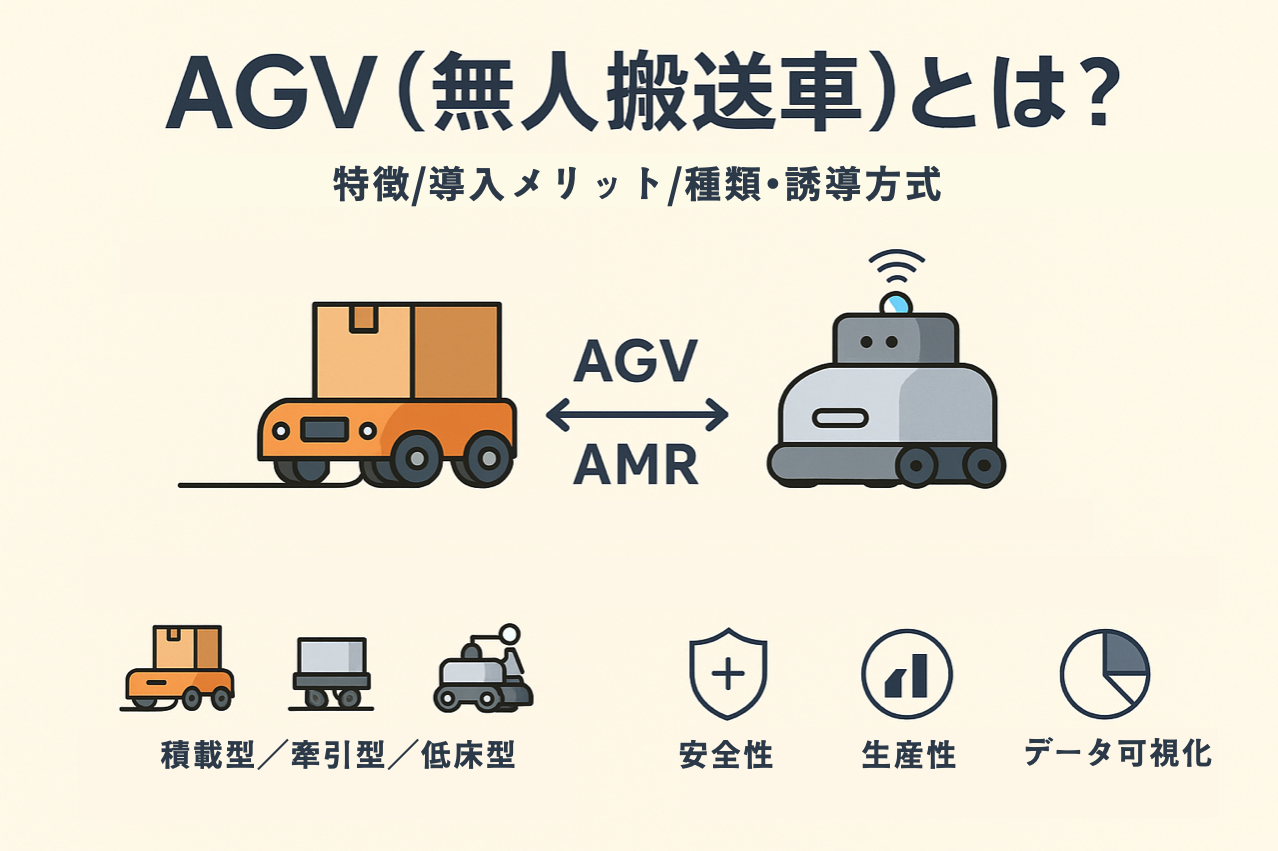

AGV(無人搬送車)とは?特徴や導入メリットについて分かりやすく解説

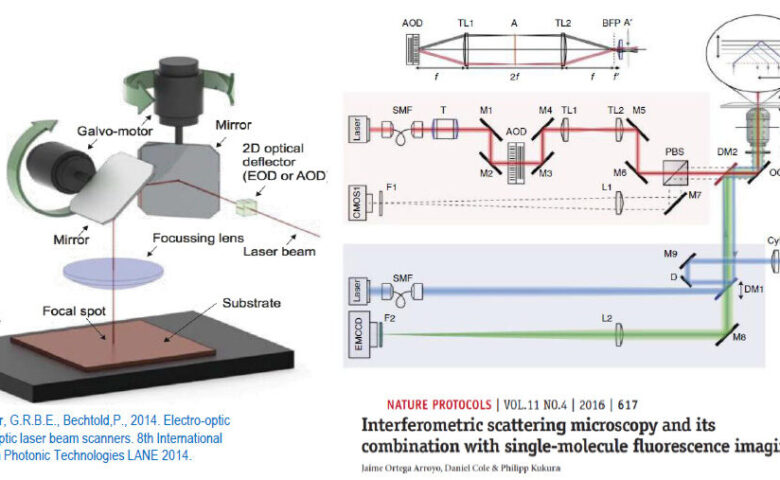

AOD(音響光学偏向器)とは?AOMとの違いも解説