- INDEX目次

目次【非表示】

- 1.EDAツールが電子設計で担う3つの主な役割

- 1-1.設計思想を具体化する「フロントエンド設計」

- 1-2.物理的なレイアウトを作成する「バックエンド設計」

- 1-3.設計上の問題を検出する「検証・シミュレーション」

- 2.半導体開発の進化にEDAツールが不可欠な理由

- 2-1.電子回路の複雑化・高集積化への対応

- 2-2.開発期間の短縮と市場投入の迅速化

- 3.EDAツール導入によって得られる4つのメリット

- 3-1.設計プロセスの効率化による開発期間の短縮

- 3-2.シミュレーションによる手戻りの削減と品質向上

- 3-3.人的ミスの防止による設計精度の向上

- 3-4.試作品製作コストの削減

- 4.【シェアトップ3】主要なEDAツールのベンダーを紹介

- 4-1.Synopsys (シノプシス)

- 4-2.Cadence (ケイデンス)

- 4-3.Siemens EDA (旧Mentor Graphics)

- 5.自社に最適なEDAツールを選ぶためのポイント

- 5-1.設計対象やプロジェクトの規模に適しているか

- 5-2.導入コストと維持・運用コストを比較検討する

- 5-3.サポート体制や技術者育成の環境が整っているか

- 6.まとめ

- 7.用語まとめ

EDAツールとは、電子機器や半導体の設計、検証、製造プロセスを自動化・効率化するためのソフトウェアの総称です。Electronic Design Automationの頭文字をとったもので、回路図作成、レイアウト設計、シミュレーション、検証など、多岐にわたる工程で活用されています。具体的には、集積回路(IC)やプリント基板(PCB)などの複雑な電子回路を効率的に設計するために必要不可欠な技術であり、現代の電子機器開発を支える基盤となっています。手作業では非常に時間と労力がかかる設計作業を、EDAソフトが自動化することで、設計者はより高度な技術的課題に集中できるようになります。この技術がなければ、現在の高性能なスマートフォンやPCなどの電子機器は実現不可能といえるでしょう。

EDAツールが電子設計で担う3つの主な役割

EDAツールは、電子設計プロセスにおいて主に3つの役割「フロントエンド設計」「バックエンド設計」「検証・シミュレーション」を担っています。

設計思想を具体化する「フロントエンド設計」

EDAツールにおけるフロントエンド設計とは、半導体や電子回路の論理的な動作を設計する初期段階を指します。このプロセスでは、デバイスがどのような機能を発揮するかを具体的に定義し、それを実現するための回路の骨格を構築します。フロントエンド設計では、主に以下の作業が行われます。

1. 回路図エディタを用いた論理設計:

設計者は回路図エディタというツールを使用して、電子回路の論理的な構成を図として表現します。これは、どのような部品を使い、それらをどのように接続するかを示す「設計思想の具体化」とも言える重要な工程です。例えば、Cadenceの「Virtuoso Schematic Editor」やSynopsysの「VCS」といったツールが活用されます。

2. HDL(ハードウェア記述言語)による設計:

VHDLやVerilogといったハードウェア記述言語を用いて、回路の動作や構造を記述します。これにより、複雑な回路でも効率的に設計・検証することが可能になります。

3. 論理シミュレーションによる動作検証:

設計した回路が意図した通りに動作するかを、シミュレーションツールを使って検証します。この段階で機能的な問題を早期に発見し、修正することで、後工程での手戻りを削減し、開発期間の短縮とコスト削減に繋げます。

フロントエンド設計で作成されたデータは、後工程であるバックエンド設計へと引き継がれ、物理的なレイアウト設計の基盤となります。このように、EDAツールは、抽象的な設計思想を具体的な回路図やHDLコードへと変換し、その動作を検証することで、複雑化する電子設計プロセスの効率化と精度向上に不可欠な役割を担っているのです。

物理的なレイアウトを作成する「バックエンド設計」

バックエンド設計は、電子回路の物理的なレイアウトを具体化する工程です。フロントエンド設計で作成された論理回路設計に基づき、実際にチップ上に構成要素を配置し、配線を行います。具体的には、回路構成要素の効率的な配置計画(Placement)や、各部品が正しく接続されるための配線設計(Routing)がこの段階に含まれます。このプロセスを最適化することで、チップの性能や消費電力の向上、さらには製造における歩留まりの改善が可能となります。

この工程では、論理設計で得られた回路情報(ゲートレベルのネットリストなど)を元に、物理的な設計ルールや制約を考慮しながら、トランジスタやゲートといった数億個にも及ぶ微細な機能ブロックをチップ上の最適な位置に配置し、それらを配線で結びつけます。 かつては熟練エンジニアが数日かけていた配置作業も、EDAツールを活用することで数時間で完了できるケースもあります。

代表的なバックエンド設計ツールには、Synopsysの「IC Compiler」やCadenceの「Innovus」などがあります。 これらのツールは、設計された回路が製造可能かどうかを確認するための物理検証(DRCやLVSなど)も行い、製造前に設計上の問題を検出・修正することで、製造コストの削減にも貢献します。

設計上の問題を検出する「検証・シミュレーション」

設計・シミュレーションは、電子回路や半導体デバイスの設計において、作成された設計が意図通りに機能するかを確認するための重要なプロセスです。EDAツールは、製造前の段階で設計上の潜在的な問題を検出し、設計エラーを早期に発見することを可能にします。これにより、設計不良による試作や製造コストの増加を防ぐことができます。

具体的には、機能検証、タイミング検証、消費電力解析、物理設計におけるレイアウト検証(DRC:Design Rule Check、LVS:Layout Versus Schematic)などが行われます。例えば、シミュレーションツール「SPICE」はアナログ電子回路の機能シミュレーションに利用され、回路図レベルで設計された回路が物理レイアウト後も寄生要素の影響で特性が変化しないかを確認できます。 また、VerilogやVHDLなどのハードウェア記述言語で記述された回路のシミュレーションを行い、論理合成前に機能的な動作を確認することも可能です。

これらの検証・シミュレーション機能により、高精度な設計と信頼性の高い製品開発を実現し、物理的な試作回数を削減することで、開発期間の短縮とコスト削減に大きく貢献します。 さらに、EDAツールはAIチップ設計のような複雑なシステム設計においても、高性能なプロセッサ開発を加速させるために不可欠な要素となっています。

半導体開発の進化にEDAツールが不可欠な理由

現在の半導体開発において、EDAツールは不可欠な存在となっています。これは、半導体が搭載される電子機器の機能向上に伴い、回路規模が飛躍的に増大し、設計の複雑化が著しいことが主な理由です。手作業での設計では時間とコストがかかり、また、人為的なミスが発生するリスクも高まります。EDAツールは、設計プロセスの自動化・効率化を可能にし、開発期間の短縮と市場投入の迅速化に貢献します。さらに、高度なシミュレーション機能により、試作段階での問題を事前に検出し、手戻りの削減と品質向上を実現できるため、現在の半導体開発には欠かせないツールです。

電子回路の複雑化・高集積化への対応

現代の電子回路は、スマートフォンやAIチップ、自動運転システムなどに搭載される半導体デバイスの性能向上に伴い、非常に複雑化し、集積度も高まっています。1970年代には数千個だったトランジスタ数が、現在では数百億個に達しており、手作業による設計はもはや現実的ではありません。

このような背景から、EDAツールは、複雑な回路設計や検証プロセスを自動化し、設計効率を飛躍的に向上させるために不可欠な存在となっています。例えば、回路図の作成、シミュレーション、レイアウト設計、検証といった多岐にわたる設計工程をサポートし、設計者は手作業では不可能なレベルの複雑な回路を効率的に設計できるようになりました。

また、EDAツールは、設計プロセスの早い段階でエラーを検出し修正することで、製造後の手戻りを削減し、品質向上にも貢献しています。さらに、過去の設計データの再利用を容易にすることで、開発期間の短縮とコスト削減を実現し、企業の競争力強化にも繋がっています。

開発期間の短縮と市場投入の迅速化

現代の半導体開発において、EDAツールは開発期間の短縮と市場投入の迅速化に不可欠な存在となっています。半導体技術の急速な進化により、ICチップに搭載されるトランジスタの数は飛躍的に増加し、設計の複雑性は増すばかりです。1970年代には手作業で行われていた数千個のトランジスタの配置・配線が、現代では数百億個にも及ぶため、人手による設計は現実的に不可能です。

EDAツールは、このような複雑な設計プロセスを自動化・効率化することで、開発期間を劇的に短縮します。手作業で数カ月かかっていた設計プロセスが、最新のEDAツールを活用することで数日、あるいは数時間にまで短縮されることも珍しくありません。この技術革新は、大手半導体メーカーが革新的な設計に特化し、製造を外部委託することで競争力を維持する上で重要な役割を担っています。

半導体業界では、スマート製品の普及や技術革新の加速に伴い、製品のライフサイクルが短縮傾向にあります。これにより、企業は短い納期で高品質な製品を提供する必要に迫られています。EDAツールは、設計プロセスの効率化と自動化を推進し、開発期間の短縮と競争力の向上に大きく貢献しています。特に、AIやIoTデバイス、モバイルデバイスの進化に伴う半導体需要の増加は、複雑なデバイス設計を迅速かつ効率的に行うための基盤として、EDAツールの重要性を一層高めています。

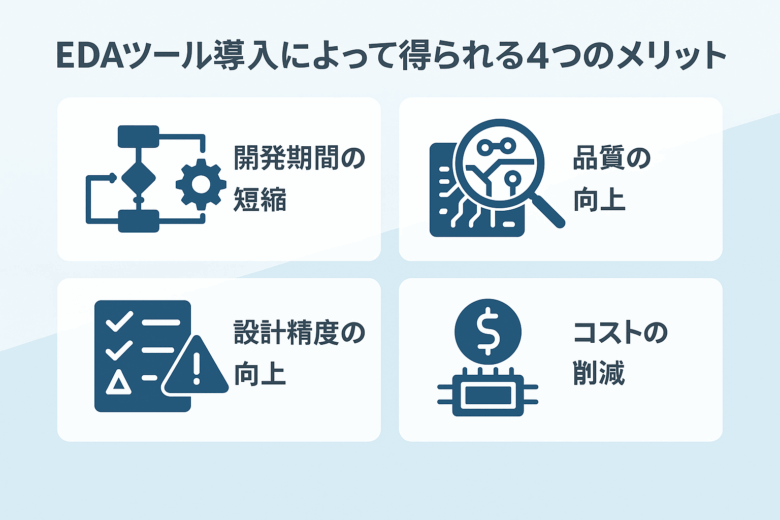

EDAツール導入によって得られる4つのメリット

EDAツールを導入することで、電子回路設計において複数のメリットが期待できます。まず、設計プロセス全体の自動化・効率化により、開発期間を大幅に短縮できます。これにより、製品の市場投入を迅速化し、企業の競争力向上につながるでしょう。

次に、堅牢なシミュレーション、検証、テスト機能が提供されるため、製造前に機能やタイミング、消費電力などを検証できます。これにより、製造後のエラー発生リスクを低減し、試作品の製作回数を削減することで、開発コストの抑制と品質の向上を実現します。

さらに、多くの設計ステップが自動化されることで、手動による人的ミスを防ぎ、設計の一貫性と精度を高めることが可能です。加えて、過去の設計データを容易に再利用できるため、効率的な開発が可能になり、余計な試作を避けることでコスト削減にも貢献します。

設計プロセスの効率化による開発期間の短縮

EDAツールの導入は、半導体や電子回路の設計プロセスを大幅に効率化し、結果として開発期間の短縮に直結します。手作業による設計では、回路が複雑になるほど時間と労力がかかり、設計ミスも発生しやすくなります。しかし、EDAツールを活用することで、回路図の作成から配置・配線、シミュレーション、検証までの一連の作業を自動化・半自動化できるため、開発者はより高度な設計業務に集中することが可能です。例えば、かつて数週間から数ヶ月を要した工程が、EDAツールによって数日から数時間で完了するケースも少なくありません。この効率化は、製品の市場投入までの時間を大幅に短縮し、競争の激しいエレクトロニクス市場において企業の優位性を確立する上で非常に重要な要素となります。特に、AIやIoTといった最新技術を搭載した製品の開発では、迅速な市場投入が成功の鍵となるため、EDAツールによる開発期間の短縮は不可欠であると言えるでしょう。

シミュレーションによる手戻りの削減と品質向上

EDAツールにおけるシミュレーション機能は、設計プロセスの早い段階で回路の機能、タイミング、消費電力などを検証することを可能にします。これにより、物理的な試作品を製作する前に設計上の問題点を特定し、修正できます。従来の電子回路設計では、試作品を製作してから評価・検証を行うことが一般的でしたが、この方法では問題が発見された際に設計に手戻りが発生し、開発期間の長期化やコスト増加の要因となっていました。

特に、集積回路やプリント基板の複雑化が進む現代において、手動での設計や検証は現実的ではありません。EDAツールによるシミュレーションは、このような複雑な設計においても高い精度で動作を予測し、製造後のエラー発生リスクを大幅に低減します。また、物理試作の回数を減らすことで、製造コストだけでなく、試作にかかる時間やリソースの節約にも貢献します。結果として、開発期間の短縮、設計精度の向上、そして製品全体の品質向上を実現できるのです。

人的ミスの防止による設計精度の向上

電子設計において、人的ミスは回路の誤動作や性能低下、さらには製品のリコールといった重大な問題を引き起こす可能性があります。EDAツールは、こうした人的ミスを未然に防ぎ、設計精度を大幅に向上させるための強力な手段です。例えば、回路図の作成やシミュレーション、レイアウト設計など、多岐にわたる設計工程を自動化することで、人手による作業で発生しがちな見落としや誤入力を削減します。

具体的には、EDAツールはフールプルーフ設計の考え方を取り入れており、ミスを誘発しにくい仕組みを提供します。例えば、設計ルールチェック(DRC)機能は、あらかじめ設定された設計規則に反する箇所を自動で検出し、設計者が早期に修正できるように促します。これにより、設計の早い段階でエラーを発見し、手戻りの削減と品質向上に貢献するのです。さらに、シミュレーション機能を用いることで、実際に試作品を製作する前に回路の動作を仮想的に検証できるため、設計ミスによるコストや時間のロスを防ぎ、設計品質を高めることができます。

このように、EDAツールは自動化と検証機能によって人的ミスを防止し、電子回路の複雑化・高集積化が進む現代において、高精度な設計を実現するための不可欠なツールとなっています。

試作品製作コストの削減

EDAツールを導入することで、試作品製作にかかるコストを大幅に削減できます。従来の手作業による設計では、回路が複雑化するほど設計ミスが発生しやすく、物理的な試作を何度も繰り返す必要がありました。しかし、EDAツールを活用することで、高精度なシミュレーションと検証を設計段階で実施できるため、物理試作の回数を最小限に抑えられます。これにより、製造コストだけでなく、試作にかかる時間とリソースも節約できます。

例えば、大規模集積回路(LSI)の設計では、手作業では数ヶ月かかるプロセスが、EDAツールを導入することで数週間程度に短縮されることもあります。また、設計プロセスの早い段階でエラーを検出・修正できるため、設計不良が原因で試作や製造コストが増加する事態を防ぐことができます。過去の設計データを再利用できる機能も、効率的な開発と余計な試作の回避に貢献し、結果として全体的な開発コストの削減につながるのです。

【シェアトップ3】主要なEDAツールのベンダーを紹介

電子設計自動化(EDA)ツール市場は、Synopsys、Cadence、Siemens EDA(旧Mentor Graphics)の3社が世界シェアの大半を占める寡占市場です。この3大ベンダーで市場の約75%を支配しているとされています。SynopsysはEDA業界のリーダーとして幅広い設計および検証ツールを提供し、特に論理合成ツールで強いシェアを誇っています。Cadenceはデジタル、アナログ、ミックスドシグナル設計において幅広いソリューションを展開しており、IC設計および検証ツール分野で存在感を示しています。Siemens EDAはIC設計からPCB設計まで多様なツールを提供し、特に電子回路基板設計ソリューションにおいてマーケットリーダーの地位を確立しています。これらの主要ベンダーは、買収などを通じて事業を拡大し、市場での優位性を維持しています。

Synopsys (シノプシス)

Synopsysは、電子設計自動化(EDA)ソフトウェアのリーディングカンパニーであり、特にデジタル設計および検証ツールにおいて高い評価を得ています。同社のツールは、半導体の設計から製造までのあらゆる工程をカバーしており、特に最先端のプロセスノードに対応する技術力は業界内でも群を抜いています。例えば、ASICやSoCなどの複雑なLSI設計において、設計期間の短縮と品質向上に大きく貢献しています。また、IP(Intellectual Property)コアの提供も積極的に行っており、顧客は自社で一から設計することなく、既存の機能ブロックを活用することで開発効率を向上させることが可能です。例えば、USBやPCI ExpressなどのインターフェースIPや、プロセッサIPなどが挙げられます。Synopsysは、AIや機械学習を活用した次世代のEDAソリューション開発にも注力しており、今後も半導体業界の発展を牽引していくことが期待されています。同社の技術は、スマートフォンやデータセンター、自動車など、私たちの生活に不可欠な様々な電子機器の進化を支えています。

Cadence (ケイデンス)

Cadence Design Systemsは、1988年にアメリカのカリフォルニア州サンノゼで設立されたEDAツールベンダーです。Synopsysと並び、EDAツール業界の主要企業の一つとして、IC設計および検証ツール分野で大きな存在感を示しています。回路設計からレイアウト設計、検証まで一貫したソリューションを提供しており、特にアナログ設計や物理設計の分野で高い評価を得ています。2024年のEDAツール市場において、Cadence Design SystemsとSynopsysは合わせて市場の30~35%のシェアを占めており、Cadence Design Systemsは業界トップクラスの企業の一つです。

Cadenceは「Intelligent System Design」という戦略を掲げており、その中核としてAI技術を積極的にEDAツールに取り入れています。例えば、AIを活用した設計プラットフォーム「Cadence.AI」を開発し、チップからシステムまでの設計と検証の自動化を推進しています。また、最適化にかかる時間を大幅に短縮するソリューション「Optimality Intelligent System Explorer」も提供しており、AI技術(強化学習)によって、設計の最適化を従来の10倍、一部の設計では最大100倍高速化することが可能です。

主な製品としては、アナログ回路設計の定番ツールである「Virtuoso」や、高性能なアナログ・RF回路シミュレーションを実現する「Spectre」、物理設計ツールである「Innovus」、プリント基板設計ツールである「Allegro」などが挙げられます。特に「Virtuoso」は、フルカスタム集積回路設計用のプログラムとして、アナログ回路、高周波、デジタルアナログ混載、スタンダードセルに対応しており、メモリやFPGA設計でも使用されています。また、「Allegro」は、高密度多層基板や高速デジタルデザインなどの複雑なプリント基板設計に対応しています。

近年では、TSMCやIBMといった大手半導体メーカーとの連携を強化し、最先端のプロセスノードにおけるAI駆動型設計フローの開発を進めています。さらに、電子設計と機械設計をシームレスに連携させるため、Autodeskとの協業により、PCB設計ツール「Allegro X」および「OrCAD X」とAutodeskの3D CAD/CAM/CAEソフトウェア「Fusion」を統合したソリューションも提供しています。

Siemens EDA (旧Mentor Graphics)

Siemens EDAは、ドイツの大手電機メーカーであるシーメンスグループの一員で、電子設計自動化(EDA)ソフトウェアとハードウェアを提供するテクノロジーリーダーです。元々はMentor Graphicsという独立したEDAベンダーでしたが、2016年にシーメンスによって買収され、現在の名称となりました。この買収により、Mentor GraphicsのEDA技術はシーメンスのデジタルインダストリーズソフトウェアの一部門として統合されています。

Siemens EDAは、特にデジタル設計、検証、そしてDesign for Test(DFT)およびテストソリューションにおいて強みを持っています。DFTツールであるTessent™は業界をリードしており、スキャン設計やメモリBIST(組み込み自己テスト)など、多様なDFT技術に対応しています。 また、物理検証ツール「Calibre」や機能検証ツール「Questa」、PCB設計ツール「Xpedition」なども主要な製品として知られています。

シーメンスによるMentor Graphicsの買収は、産業向けソフトウェアポートフォリオを強化し、製品ライフサイクル管理(PLM)との連携を深めることを目的としていました。これにより、チップ、基板、電気/電子(E/E)システムのデータを設計、製造、クラウド間で自由に移動させることが可能な、クローズドループのデジタルツイン管理を実現しています。 シーメンスEDAは、半導体開発の複雑化に対応し、次世代テクノロジーノードへの移行を予測可能な結果で支援することを目指しています。

自社に最適なEDAツールを選ぶためのポイント

自社に最適なEDAツールを選定する際は、まず設計対象となる製品やプロジェクトの規模に合っているかを確認することが重要です。次に、導入にかかる初期費用と、その後の運用・維持にかかるコストを総合的に比較検討し、費用対効果を見極める必要があります。大手半導体企業の場合、EDAツールに年間数千万ドルを費やすケースもあり、コストは企業収益の1~1.5%にも相当するといわれています。最後に、ベンダーのサポート体制や技術者育成の環境が整っているかも重要な判断基準です。ツールの操作方法に関する支援だけでなく、エンジニアの教育支援や回路・基板設計の受託など、包括的なサポートが提供されているかを確認することをおすすめします。

設計対象やプロジェクトの規模に適しているか

EDAツールを選定する際は、まずご自身の設計対象やプロジェクトの規模に合致しているかを確認することが重要です。EDAツールは非常に多岐にわたる種類と用途があり、小規模な設計には使いやすさとコストパフォーマンスを重視したツールが適している一方、大規模な設計や最新のプロセスノードを扱う場合は、フルカスタム設計に対応できる高度なツールが必要になります。

例えば、複雑な半導体設計を行う場合は、SynopsysやCadence、Siemens EDAといった主要ベンダーのツールが提供する、幅広い設計および検証ソリューションが役立ちます。これらのツールは、回路設計からレイアウト設計、検証まで一貫したフローを提供し、特にアナログ設計や物理設計の分野で高い評価を得ています。 また、FPGA向けのEDAツールであれば、RTLデザインからインプリメンテーション、デバッグまで、設計フローに必要なすべての機能を統合したツールスイートを選ぶことで、開発効率を大幅に向上できる場合があります。

プロジェクトの規模や設計の複雑さに応じて、適切な機能と性能を持つEDAツールを選ぶことで、設計プロセスの効率化、品質向上、開発期間の短縮、人的ミスの防止、そして試作品製作コストの削減といったメリットを最大限に享受することができます。 導入前に、具体的な設計要件を明確にし、それに最適なツールを見極めることが成功の鍵となります。

導入コストと維持・運用コストを比較検討する

EDAツールを導入する際は、初期費用だけでなく、長期的な運用を見据えたコスト比較が不可欠です。例えば、無料のオープンソースEDAツールは導入コストを抑えられますが、機能が限定的であったり、技術サポートが不足していたりする場合があります。一方、高機能な商用EDAツールは導入コストが高額になりがちですが、ベンダーによる充実したサポートや定期的なアップデートが提供されるため、結果的に長期的な運用コストを抑えられる可能性があります。

特に、クラウドベースのEDAツールは、初期投資を抑えつつ、必要な時に必要なリソースを利用できるため、柔軟なコスト管理が可能です。ライセンス形態も年間契約や従量課金制など多様化しており、プロジェクトの規模や利用頻度に合わせて最適なプランを選択することが重要です。導入コストと維持・運用コストを総合的に評価し、自社の予算とニーズに合致するEDAツールを選定しましょう。

サポート体制や技術者育成の環境が整っているか

EDAツールを最大限に活用するためには、導入後のサポート体制と技術者育成環境が非常に重要です。ベンダーが提供するサポート体制は、技術的な問題が発生した際に迅速な解決を支援し、設計スケジュールへの影響を最小限に抑える上で不可欠となります。FAQやオンラインリソースの充実度も、自己解決能力を高める上で重要な要素です。

また、新しいEDAツールを導入する際には、設計者への教育が欠かせません。ツールを効果的に使いこなすためには、基本操作から応用方法までを習得できるトレーニングプログラムの計画が必要です。多くのEDAベンダーは、オンライン、クラスルーム、オンサイトなど多様な形式でトレーニングを提供しています。例えば、シーメンスEDAではCalibreやXpeditionといった製品のトレーニングを行っており、オンデマンドトレーニングライブラリやデジタルバッジの取得機会も提供しています。

さらに、社内で専門知識を持つ「スーパーユーザー」を育成することで、ツール活用の幅が広がり、組織全体のスキルアップにも繋がります。外部のトレーニングコースやセミナー、ハンズオンワークショップを活用することも、効率的なスキルアップに有効です。

最近では、技術研究組合 最先端半導体技術センター(LSTC)がNEDOの委託事業として、Synopsys社やCadence社の最先端EDAツールを使いこなすスペシャリストの育成を目的とした無料の初級コースを提供するなど、半導体設計人材育成に向けた取り組みも進められています。

まとめ

EDAツールは、電子回路や半導体デバイスの設計プロセスを自動化・効率化するソフトウェア群の総称です。主に、設計思想を具体化するフロントエンド設計、物理的なレイアウトを作成するバックエンド設計、設計上の問題を検出する検証・シミュレーションの3つの役割を担っています。半導体開発の複雑化や開発期間の短縮が求められる現代において、EDAツールは不可欠な存在です。

EDAツールの導入は、設計プロセスの効率化、シミュレーションによる手戻りの削減と品質向上、人的ミスの防止による設計精度の向上、試作品製作コストの削減といったメリットをもたらします。 EDAツール市場はSynopsys、Cadence、Siemens EDA(旧Mentor Graphics)の3社が大きなシェアを占めており、それぞれが幅広いソリューションを提供しています。

自社に最適なEDAツールを選ぶためには、設計対象やプロジェクトの規模、導入コストや維持・運用コスト、そしてベンダーのサポート体制などを総合的に検討することが重要です。

用語まとめ

1. EDAツール

Electronic Design Automationの略。電子回路や半導体設計を自動化するソフト群。設計効率を高め、開発期間を短縮する中核的存在。

2. 半導体設計

集積回路(IC)やSoCなどを設計するプロセス。EDAツールが設計・検証・レイアウトを支援し、精度とスピードを両立する。

3. フロントエンド設計

回路の論理構造や動作を定義する初期設計工程。HDLを用いて機能を具体化し、シミュレーションで検証する。

4. バックエンド設計

物理レイアウトの作成工程。チップ上のトランジスタや配線を最適配置する。性能・消費電力・歩留まりに直結する重要フェーズ。

5. HDL(ハードウェア記述言語)

VerilogやVHDLなど、電子回路の構造と動作をテキストで記述する言語。論理設計をプログラムとして扱える。

6. シミュレーション

EDAツールが設計段階で回路動作を仮想的に検証する工程。試作前にエラーを発見でき、コストと期間を削減できる。

7. DRC / LVS検証

DRCは設計ルール違反の検出、LVSは回路図とレイアウトの一致確認を行う。製造可能性を確保するための必須プロセス。

8. Synopsys

EDA業界最大手。ASIC・SoC設計で圧倒的シェアを持ち、論理合成やAI設計支援ツールを提供するリーディング企業。

9. Cadence

EDAツールのグローバルリーダーの一社。「Virtuoso」「Spectre」「Allegro」などを展開し、アナログ・デジタル両設計に強い。

10. Siemens EDA(旧Mentor Graphics)

物理検証ツール「Calibre」やPCB設計「Xpedition」で有名。PLM統合により設計〜製造をシームレスに管理できる。

11. SoC(System on Chip)

CPUやメモリを一体化した高集積チップ。EDAツールが大規模な統合設計を可能にし、AI・モバイル機器に多用される。

12. AIチップ設計

AI演算向けの専用半導体設計。EDAツールの自動最適化と機械学習解析が設計スピードと省電力化を支える。

13. クラウドEDA

クラウド環境でEDAを利用する形態。高性能計算資源をオンデマンドで使え、コスト効率と柔軟性を両立する次世代設計手法。

西進商事コラム編集部

西進商事コラム編集部です。専門商社かつメーカーとしての長い歴史を持ち、精密装置やレーザー加工の最前線を発信。分析標準物質の活用も含め、さまざまなコラム発信をします。

ファウンドリとは?半導体業界での役割やOSATとの違い、メリットを解説

フォトニクス集積とは?高速伝送・省電力を実現する技術を解説

フォトレジストとは?半導体製造の鍵を握る日本の高性能技術を解説